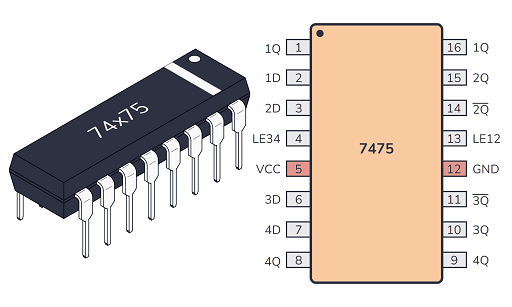

7475 74LS75 4-BIT BISTABLE LATCHES

The 74LS75 (SN74LS75) from Texas Instruments is a quad D‑latch IC based on Low‑Power Schottky TTL logic, designed for reliable temporary storage in digital systems. It captures data on inputs D1–D4 during an active Enable signal. When Enable is subsequently deactivated, the latched data is held constant on the Q outputs—even if input data changes. This feature is useful for implementing registers, bus buffers, or state-hold circuits in logic-based designs.

The complement outputs Q̄ provide both active-high and active-low logic states for flexibility in digital interfacing. The device is available in DIP‑16 and SOIC‑16 packages and is fully compatible with TTL, NMOS, and CMOS logic levels.

🛠 Technical Details

| Specification | Details |

|---|---|

| Logic Family | TTL – 74LS Series |

| Latch Type | 4 × D-type bistable (transparent latch) |

| Supply Voltage (Vcc) | 4.75 – 5.25 V typical, 5 V nominal |

| Enable Behavior | Transparent when HIGH, holds when LOW |

| Outputs | Complementary Q and Q̄ per latch |

| Propagation Delay (tpd) | ~10–15 ns typical at CL = 15 pF |

| Output Sink (IOL) | Up to 8 mA per output |

| Operating Temp Range | 0 °C to +70 °C (74LS series) |

| Input Clamp Protection | Diode-clamped inputs |

| Package Options | DIP‑16, SOIC‑16 |

| Supply Current | up to ~530 µA |

💡 Use Cases & Applications

-

Digital Registers & Buffers: Hold multi-bit data when a control signal transitions.

-

Bus Interface Logic: Stabilize data on shared buses during state transitions.

-

Signal Synchronization: Lock outputs until all input signals are valid.

-

Educational Demonstrations: Illustrate latch behavior and digital memory fundamentals.

-

Control Logic Modules: Store states in microcontroller-less automation circuits.

🛠️ Pair With

-

🧩 Electronics Components – resistors, buffers, pull‑ups

-

🛠 Tools & Accessories – testing tools such as logic probes or oscilloscopes

-

⚡ Power Supply Modules – provide clean +5 V for TTL logic

🎥 YouTube Tutorial

⚠️ Precautions & Tips

-

Use a regulated 5 V supply to ensure proper TTL-level performance.

-

Tie unused Enable and control pins to defined logic levels to prevent floating inputs.

-

Be mindful of fan-out requirements when driving TTL loads.

-

For long-term data retention, hold Enable LOW to avoid unintended overwriting.

🏁 Summary & Call-to-Action

Compact yet robust, the 74LS75 quad D‑latch IC is a trusted component for data buffering, temporary storage, and logic hold applications. With complementary outputs and TTL-level inputs, it remains a staple in legacy and modern TTL-based designs.

🛒 Order now through Electroway — stock up on essential logic chips and hardware components.

Reviews

There are no reviews yet.